W80x的GPIO速度很慢問題

W80x的主頻速度很高,用來連接彩屏,刷屏顯示應該是綽綽有餘,但是實際測試發現刷屏速度很慢。使用8BIT並口刷屏,實際測下來不如主頻跑在48MHz的STM32F030F6刷屏速度快!!!遂展開細究!

測試硬件如下:

焊接的W801芯片,但是使用W806的裸機SDK工程測試,目的是避免W801SDK工程的RTOS和中斷等功能影響測試準確性。

只測試全屏清空,屏幕分辨率為240*432,8080並口,刷屏數據為RGB565,寫兩次8bit為一個像素點。

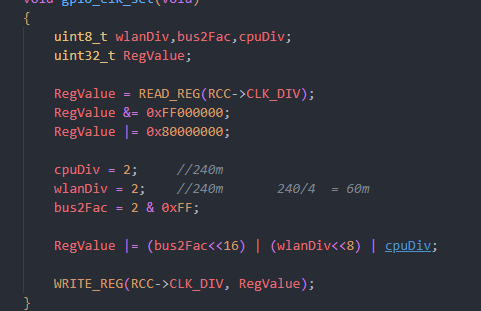

經過特殊優化後的LCD刷屏核心代碼和編譯後匯編如下:

注意,為避免誤差,優化後,每一個指令讀書寫GPIO寄存器!!!沒有多餘操作!!

一個for循環內有8個緊密相連的ST.W指令,全是單周期操作GPIO!!和一個循環跳轉指令BNEZ!!相比於正常的GPIO操作,“讀ld.w--改bseti/bclri--寫st.w”,沒有別的多餘的“讀--改”步驟,只有“寫”步驟,從理論上杜絕是因為代碼寫的稀爛導致的刷屏速度慢!也方便後續速度測試

理論計算:以上述指令ST.W均為單周期,跳轉指令BNEZ因為要清流水線視為3個周期,寫一個像素算10個CPU時鐘,以下簡稱10T。

寫240*432像素需要1036800T

在主頻跑240MHz情況下,顯示一屏需要的時間是4.32ms,也就是可以刷231.5帧/秒(暫時不考慮屏幕受不受得了)

實測,以240MHz主頻刷屏,寫一屏耗時33.6ms,慢了一個數量級,只有30帧的速度我不能接收,肉眼可見的明顯拉窗簾現象!!!實際測主頻跑在48MHz的STM32F030F6刷屏速度都可以接近50帧!

測試將W801主頻降低到80MHz,此處發現了貓膩,寫一屏耗時36.4ms,只是稍微增加?

刷屏速度沒有變慢三倍。這裡發現了貓膩。應該是GPIO速度和CPU時鐘速度不匹配。

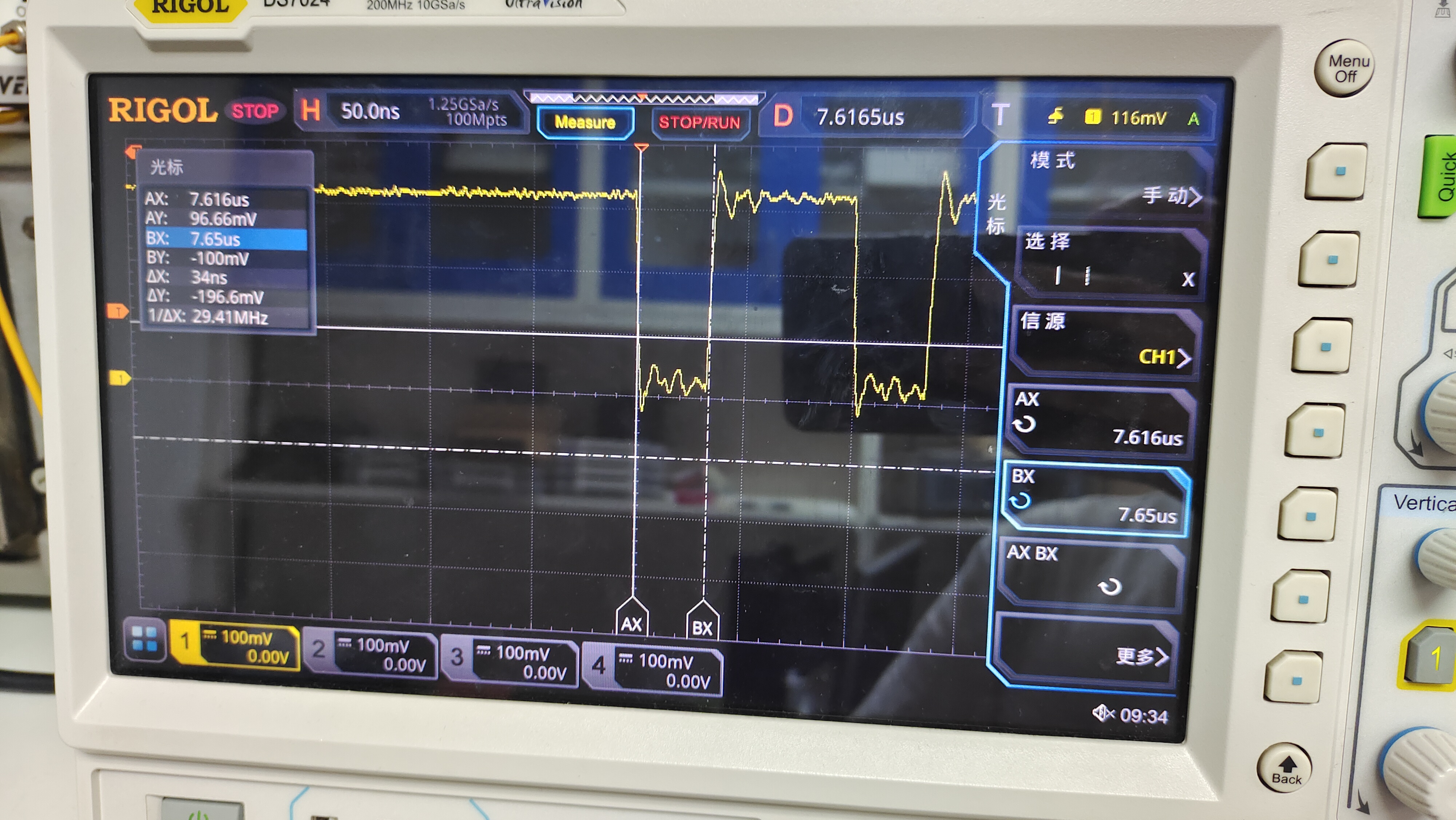

因為手上邏輯分析儀性能不足以測量IO翻轉速度,特意借用了10Gsps的示波器測試。

測量數據位引腳的波形:寫一個像素時間位360ns,也就是10T的用時,理論上10T用時應該是41ns左右

測量WR引腳的波形:這兩個時鐘之間的間隔在匯編上就表現為:

GPIOB->DATA = gpiob_cache_clr;

8011d6a: dda32000 st.w r13, (r3, 0x0)

GPIOB->DATA = gpiob_cache_set;

8011d6e: dd832000 st.w

這裡很明顯的發現,GPIO時鐘只有20MHZ????????

20MHz開什麼天才國際大玩笑的設計????!!!?這可是主頻240MHz的處理器哎!!!!怎麼說也得給個50MHz好吧??????

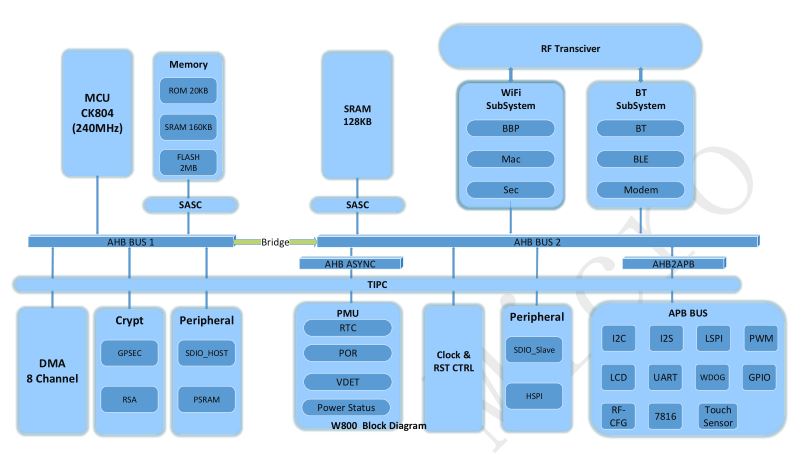

根據手冊猜測,而且CPU在訪問GPIO為啥的時候應該是AHB-AHB2-APB的路徑,寫入GPIO操作後類似於總線忙,CPU一直在死等,這就造成了20MHz這種情況的奇觀。

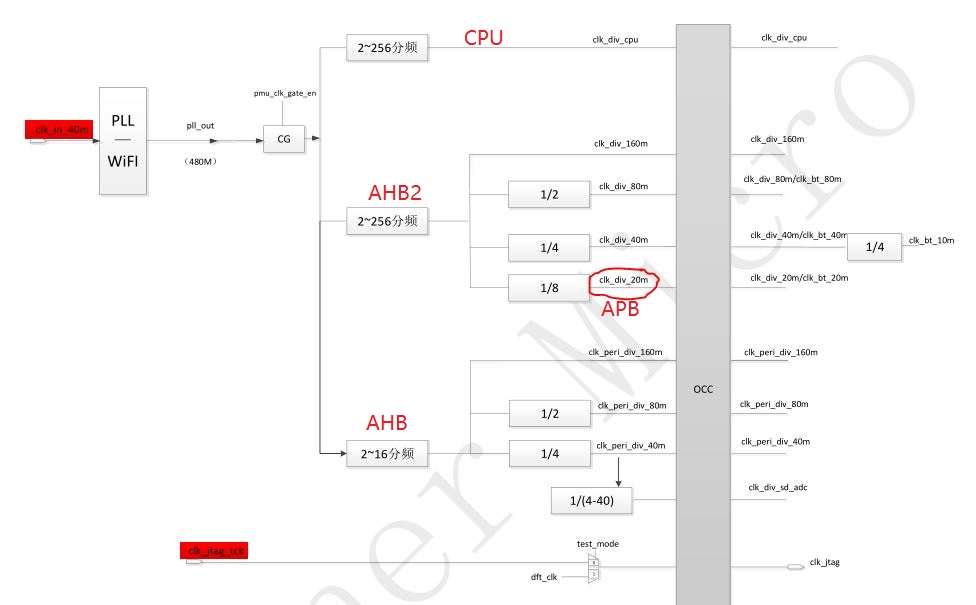

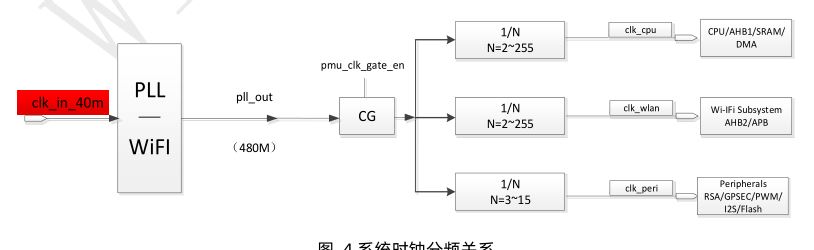

刷個屏幕拉窗簾不能接受,為了能提速,反複閱讀了寫的是中文但是不知道寫的是啥的手冊的CLK部分,明白APB時鐘居然受控於WLAN根時鐘管理???莫名其妙+1

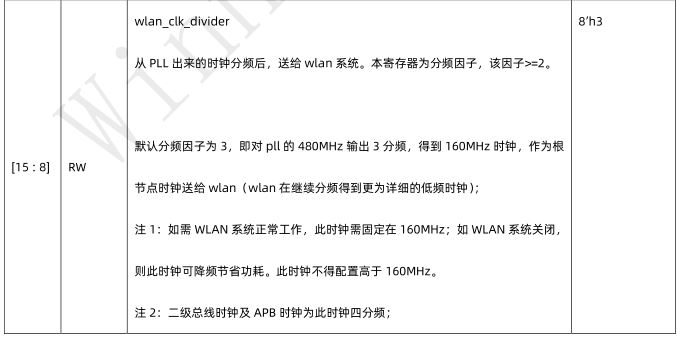

"如果希望 WLAN 系統正常工作,WLAN 根時鐘需要保持在 160MHz",二級總線時鐘及 APB 時鐘為此時鐘四分頻,這裡再2分頻就是GPIO時鐘的20MHz

將wlan根時鐘從原本的480MHz/3=160MHz調整到2分頻 240MHz。

這樣GPIO的速度就上來了,有30MHz了,如圖單周期執行33ns:

刷屏時間來到22.5ms,這個速度有40多帧,總算不拉窗簾了

現在問題來了:這樣直接超WLAN根時鐘,wifi功能肯定不能用了。

官方有辦法解決嗎?或者是開放一些時鐘分頻的配置寄存器,讓APB和AHB2不是綁定四分之一時鐘關系。

可否保留wifi功能支持的情況下,提高GPIO的速度。

主頻240MHz的單片機刷個屏幕還這麼拉跨說出去多丟人啊。。。

你說別人程序寫的爛刷屏慢可以怪用戶不會用,這問題如果官方不給出方案或者開發隱藏寄存器,換個神仙用戶也優化不了哦,總不能給你一個時鐘周期擠一擠變成兩條操作用了吧?

刷不了 刷240*320應該還勉強,超過了這個分辨率可以放棄了。或者你用16bit並口好點

SPI 串口屏240x320 最大刷到 27fps

https://www.bilibili.com/video/BV14T4y1r7FS?vd_source=08d4c5b1e3444b638e3cc29864ce3a9c#reply111349287184